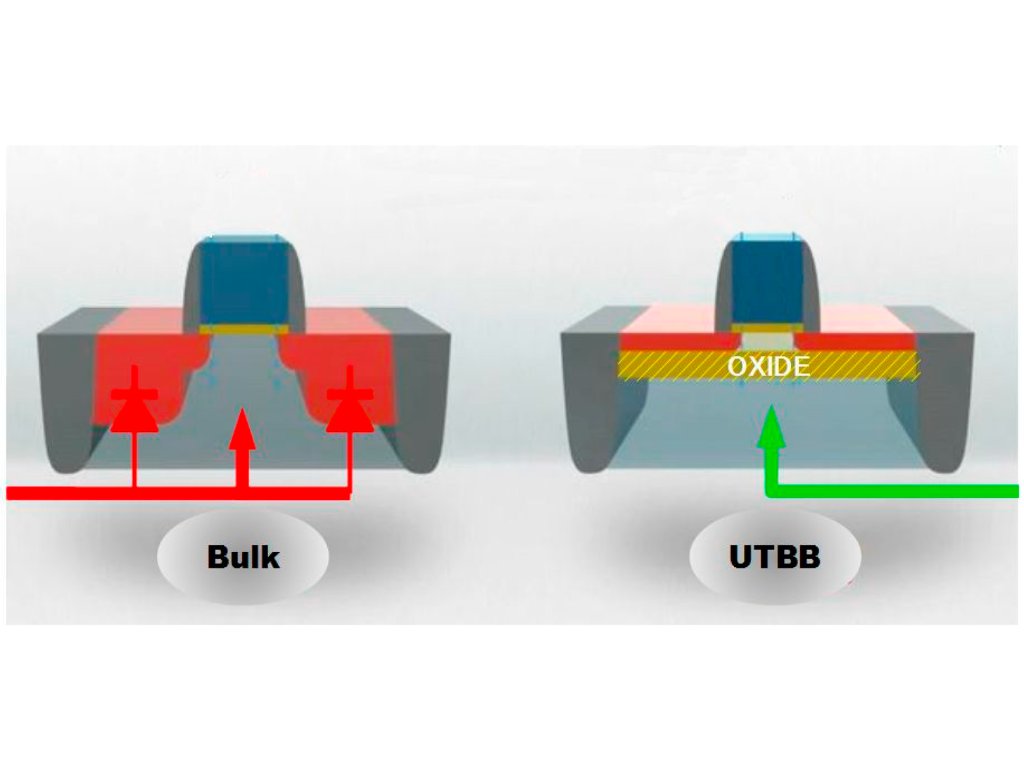

Have you harnessed @globalfoundries’ cutting-edge FDX™ FD-SOI technology yet? It features ultra-low-power, ultra-low leakage, RF and mmWave, as well as embedded non-volatile memory and automotive-qualifications all in one chip. #FDSOI #ChipDesign #GlobalFoundriesPartner

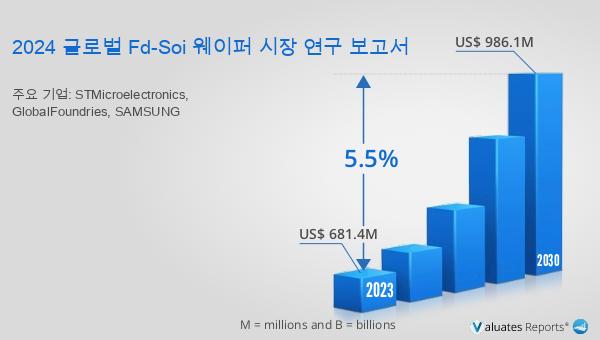

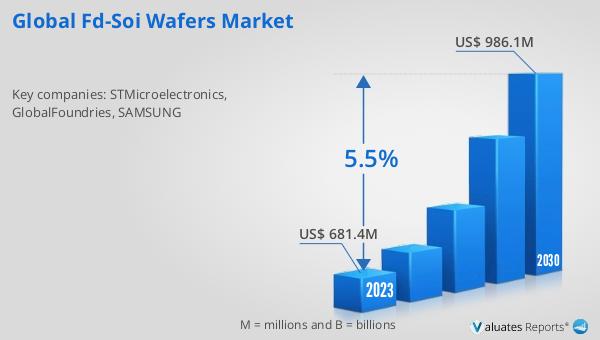

FDSOI 웨이퍼 시장의 미래를 발견하세요! 2030년까지 986.1백만 달러에 도달할 것으로 예상되며, CAGR은 5.5%입니다. 지금 바로 확인하세요: reports.valuates.com/market-reports… #GlobalFDSOIWafers #SemiconductorMarket

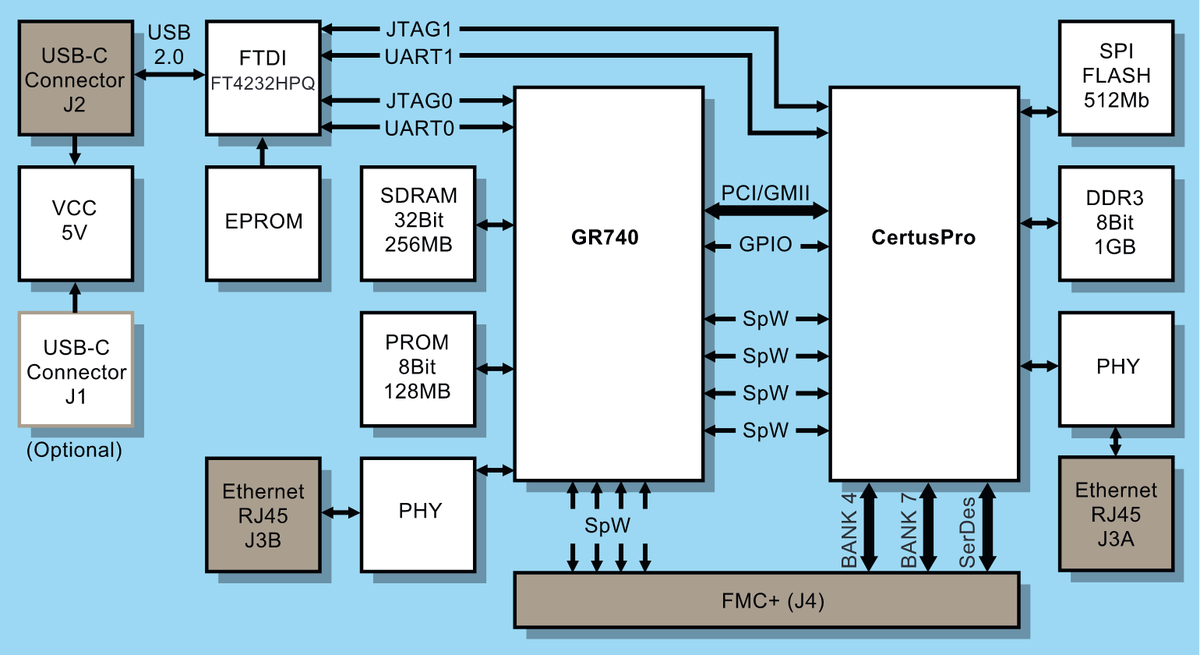

Surprisingly, The Lattice CertusPro is a great FPGA for space applications. The FDSoI technology prevents a lot of SEE-induced failures. Let's explore Fault injection, TMR, and SpaceWire with the GR740-MINI. Thanks Frontgrade Gaisler

gaisler.com/index.php/prod…

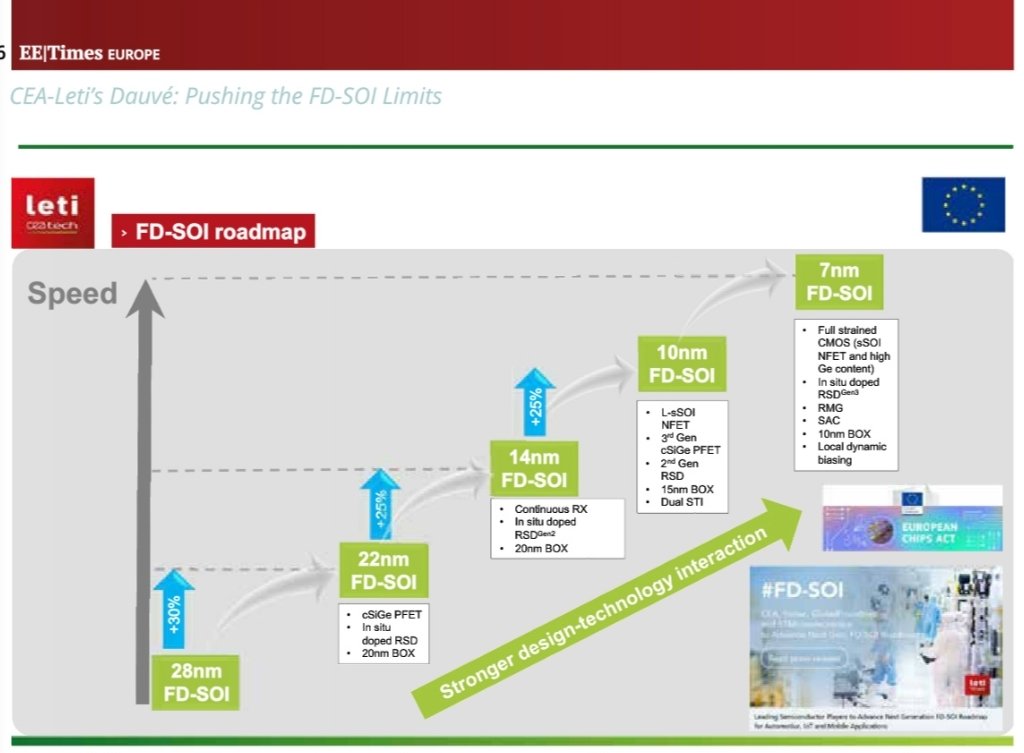

Impatient d'ecouter Soitec a TED Talks TEDxSaclay et bel article roadmap #FDSoI par EE Times Europe Anne-Francoise Pelé CEA-Leti.

eetimes.eu/ee-times-europ…

ESIEE PARIS FMD - Forschungsfabrik Mikroelektronik Deutschland imec Silicon Saxony #semiconductor #EUchipact

Discover the future of electronics with our latest market report on FDSOI Wafers! Expected to hit $986.1M by 2030, growing at a 5.5% CAGR. Dive in now: reports.valuates.com/market-reports… #GlobalFDSOIWafers #SemiconductorMarket

Our colleagues will be presenting during the RADECS poster session on Wednesday, September 27th. The title of their paper is 'LEON5FT and NOEL-VFT System on Chip: STM 28 nm FDSOI Test Chip SEE Characterization,' and it's the result of a collaboration with STMicroelectronics

🎉 Read our latest publication!

📚 'LC Tank Oscillator Based on New Negative Resistor in FDSOI Technology' by Yuqing MAO, Yoann Charlon, Yves Leduc, Gilles Jacquemod from Université Côte d'Azur

📍 mdpi.com/2079-9268/14/1…

#AnalogCircuits #FDSOITechnology #LCtankOscillator

最大化产品的灵活性能!黑盒14nm 和白盒28 FDSOI 的LPP 1G以太网PHY IP 现已正式开放授权

For More Info Visit On: t2m-ip.cn/news/1g-ethern…

#1GEthernetPHYIP #EthernetPHYIP #BlackboxLicense #Gbe #Gbe phyip #Gbe phyipcore #Gbe 10BaseTxEthernetIP #Gbe 100BaseTxEthernetIP #Gbe 1000EthernetIP

A low-power Injection-Locked Clock and Data Recovery using a 28 nm Ultra-Thin Body and Box-Fully Depleted Silicon on Insulator (UTBB-FDSOI) technology is presented in this paper. Read: mdpi.com/2079-9268/14/2…

#FDSOI #technology #semiconductor #research

Meraj Ahmet from University of Glasgow presenting Characterization of 22nm FDSOI transistors down to mK temperatures at the SQD23!

MartinWeides Prof Hadi Heidari KavehDelfanazari QuantumSensorsGlasgow UofG Electronics & Nanoscale Engineering Centre for Quantum Technology

[NEWS] With NextGen, CEA-Leti is inventing the future generations of electronic chips to maintain France’s competitiveness📈.

leti-cea.com/cea-tech/leti/…

#FDSOI #nanotechnology #cleanroom

![CEA-Leti (@CEA_Leti) on Twitter photo 2023-07-10 08:16:30 [NEWS] With NextGen, CEA-Leti is inventing the future generations of electronic chips to maintain France’s competitiveness📈.

leti-cea.com/cea-tech/leti/…

#FDSOI #nanotechnology #cleanroom [NEWS] With NextGen, CEA-Leti is inventing the future generations of electronic chips to maintain France’s competitiveness📈.

leti-cea.com/cea-tech/leti/…

#FDSOI #nanotechnology #cleanroom](https://pbs.twimg.com/media/F0qUjYOXwAADPM3.jpg)

![Wladek Grabinski (@wladek60) on Twitter photo 2023-06-13 15:16:58 [paper] H-C. Han, Z. Zhao, S. Lehmann, E. Charbon and C. Enz, 'Novel Approach to FDSOI Threshold Voltage Model Validated at Cryogenic Temperatures,' in IEEE Access, doi: 10.1109/ACCESS.2023.3283298. buff.ly/43DiMln [paper] H-C. Han, Z. Zhao, S. Lehmann, E. Charbon and C. Enz, 'Novel Approach to FDSOI Threshold Voltage Model Validated at Cryogenic Temperatures,' in IEEE Access, doi: 10.1109/ACCESS.2023.3283298. buff.ly/43DiMln](https://pbs.twimg.com/media/Fygx9kuXwAAlcq_.png)

![Wladek Grabinski (@wladek60) on Twitter photo 2023-04-06 15:44:17 [paper] G. Yu et al., 'Fully-Depleted Silicon-on-Insulator (FDSOI) Based Complementary Phototransistors for In-Sensor Vector-Matrix Multiplication,' in IEEE Electron Device Letters, vol. 44, no. 4, pp. 670-673, April 2023,

doi: 10.1109/LED.2023.3248076.

buff.ly/3Mn7pbC [paper] G. Yu et al., 'Fully-Depleted Silicon-on-Insulator (FDSOI) Based Complementary Phototransistors for In-Sensor Vector-Matrix Multiplication,' in IEEE Electron Device Letters, vol. 44, no. 4, pp. 670-673, April 2023,

doi: 10.1109/LED.2023.3248076.

buff.ly/3Mn7pbC](https://pbs.twimg.com/media/FtCsGt_XoAwUiQ_.jpg)

![Wladek Grabinski (@wladek60) on Twitter photo 2023-06-28 06:31:11 [usinenouvelle.com] Le #CEA-Leti investit plus de 500 millions d’euros dans la technologie de puces #FDSOI

[photo: Visite du commissaire européen Thierry Breton au CEA-Leti en juillet 2021] buff.ly/4431a2H [usinenouvelle.com] Le #CEA-Leti investit plus de 500 millions d’euros dans la technologie de puces #FDSOI

[photo: Visite du commissaire européen Thierry Breton au CEA-Leti en juillet 2021] buff.ly/4431a2H](https://pbs.twimg.com/media/FzsJd6BWAAEodVt.jpg)