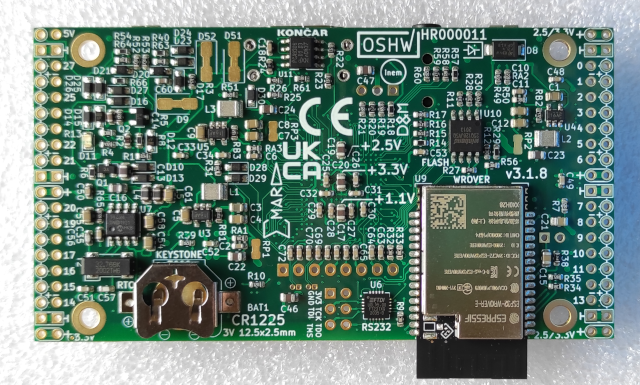

World's first XV6 RISC-V machines on ECP5 IceSugarPro and ULX3S with 32MiB SDRAM. I don't really know why? :) I will be celebrating all Sunday. #logicDestroyer

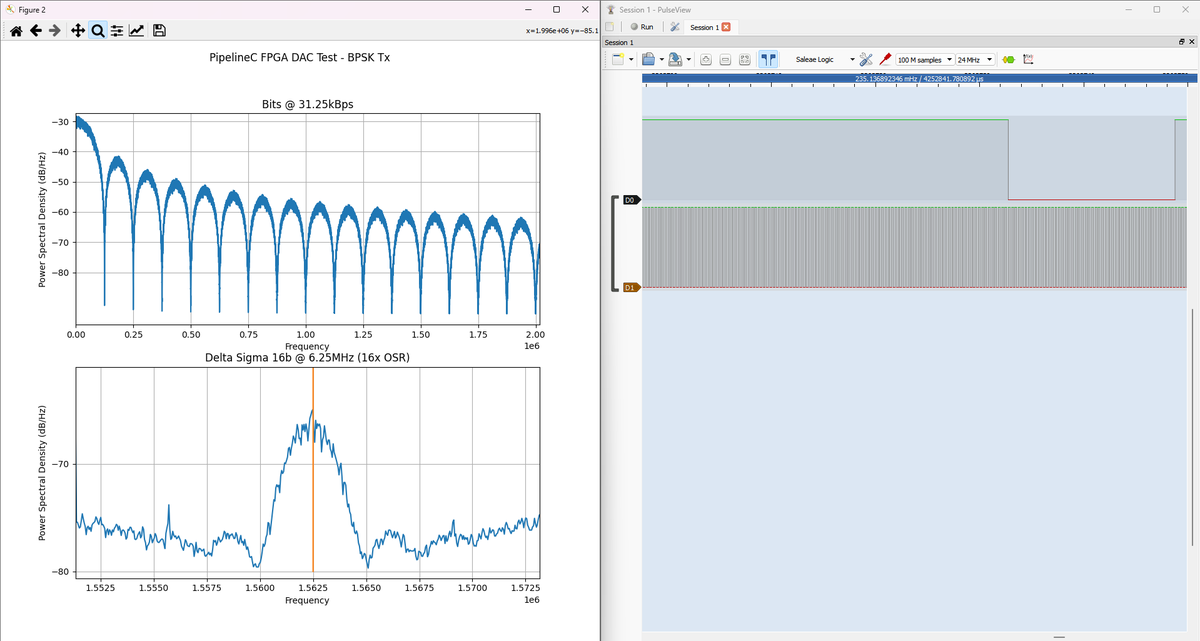

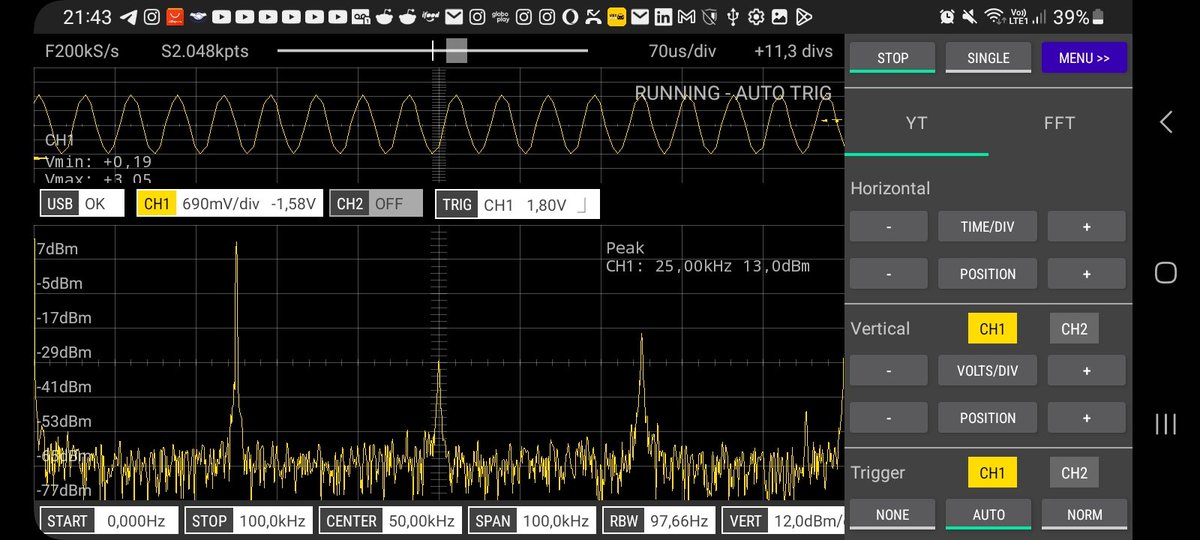

Testing the #SigmaDelta DAC made on the #ULX3S fpga using #PipelineC PipelineC (fosstodon.org/@pipelinec)

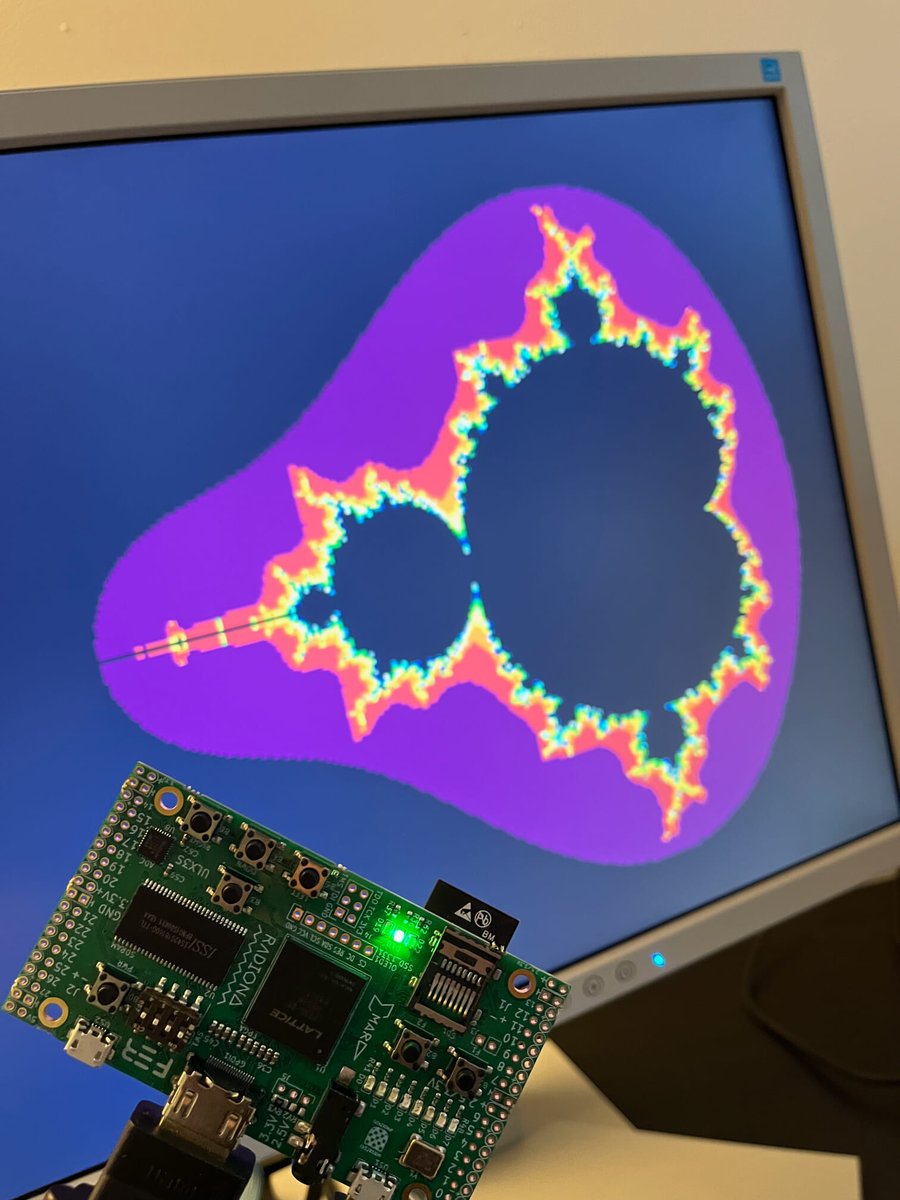

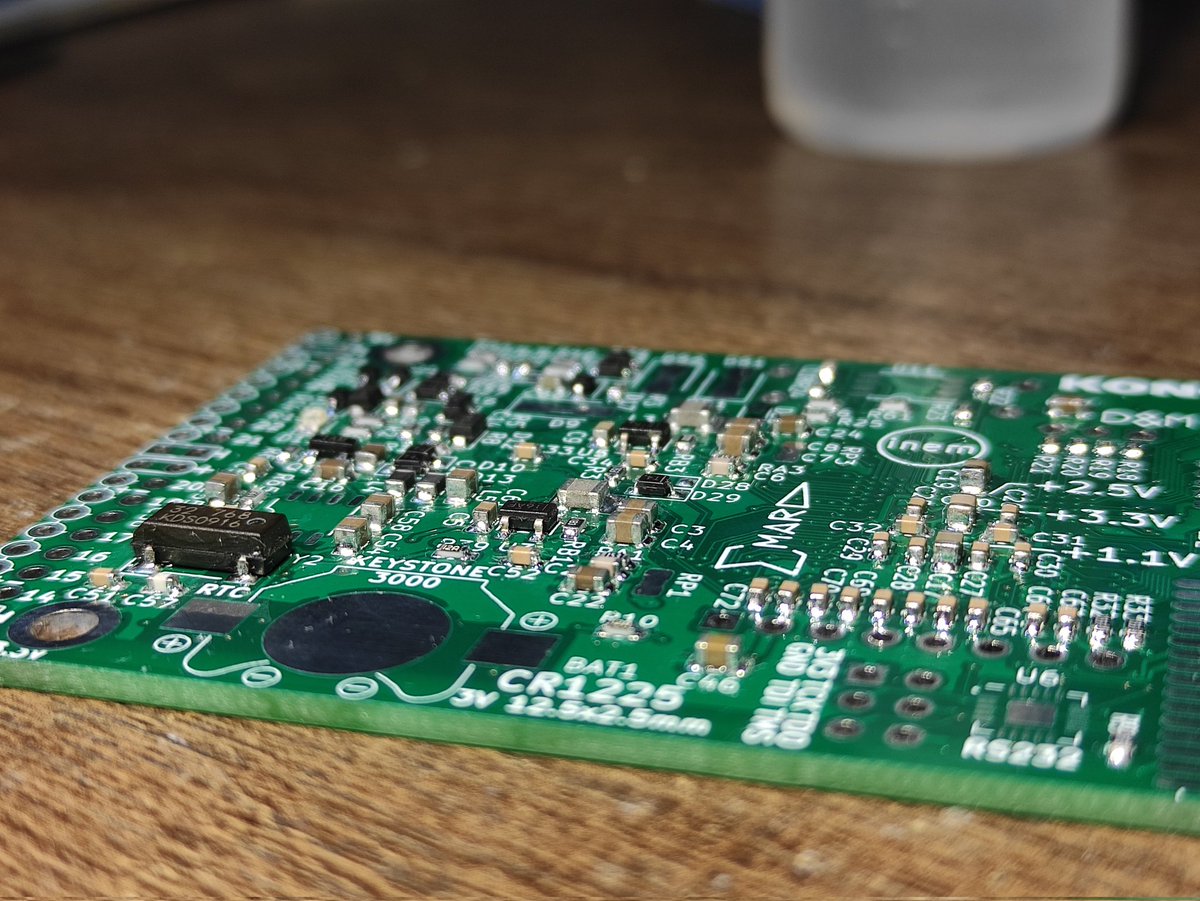

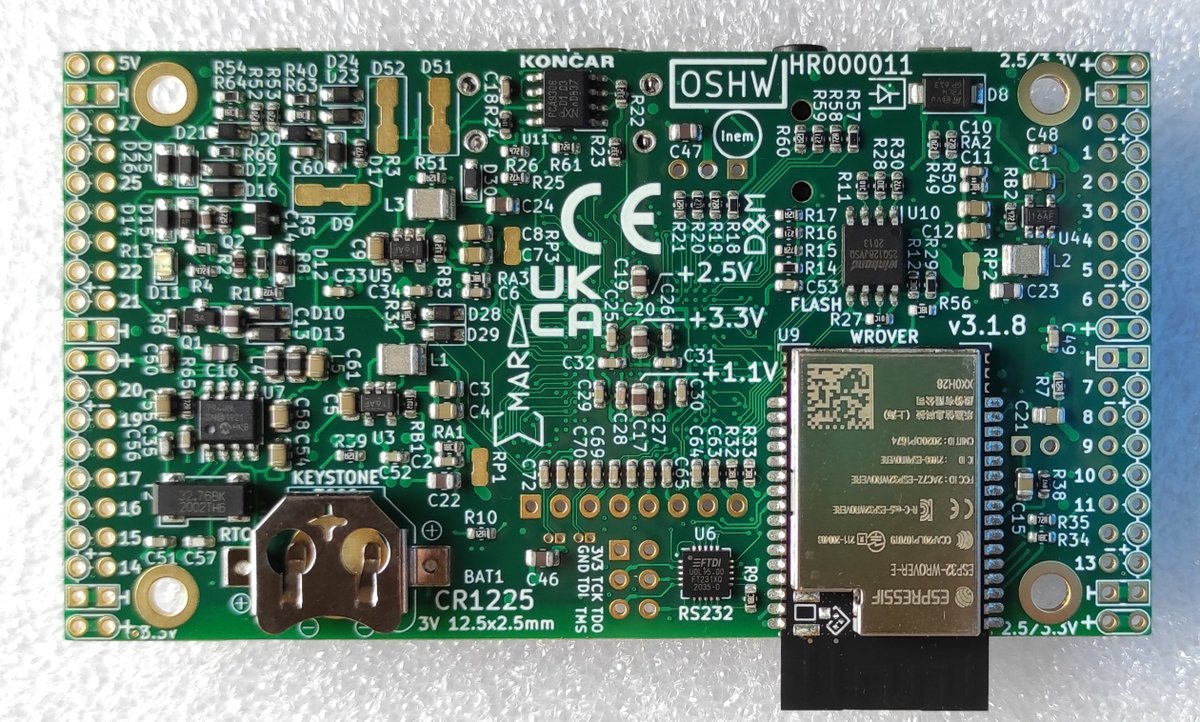

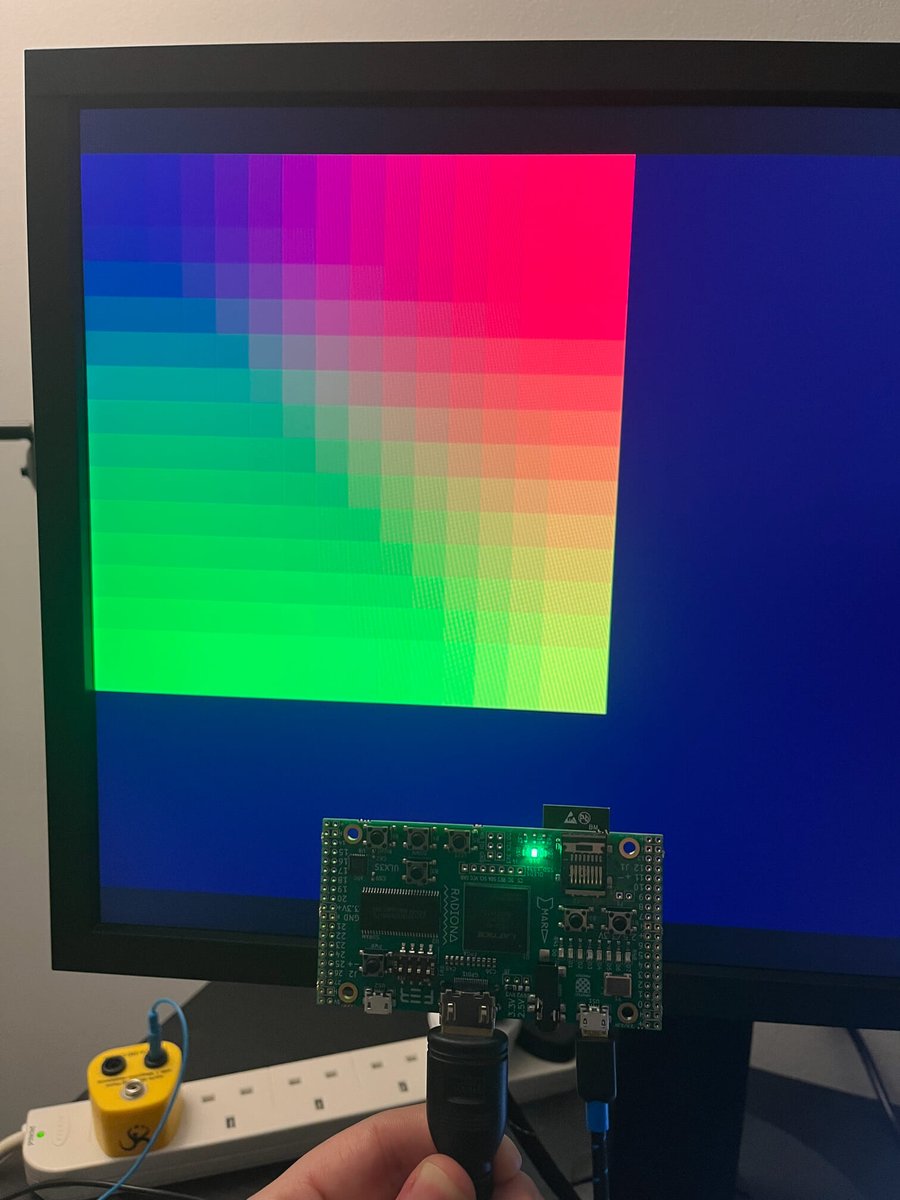

It's #FPGA Friday already! This week, I've got some 1280x720 ULX3S graphics designs for you. Please give them a try and let me know how you get on. This is my first attempt at graphics on ECP5. #FPGA Radiona_org - Zagreb Makerspace

Find the Verilog source & Makefile in git: github.com/projf/projf-ex…

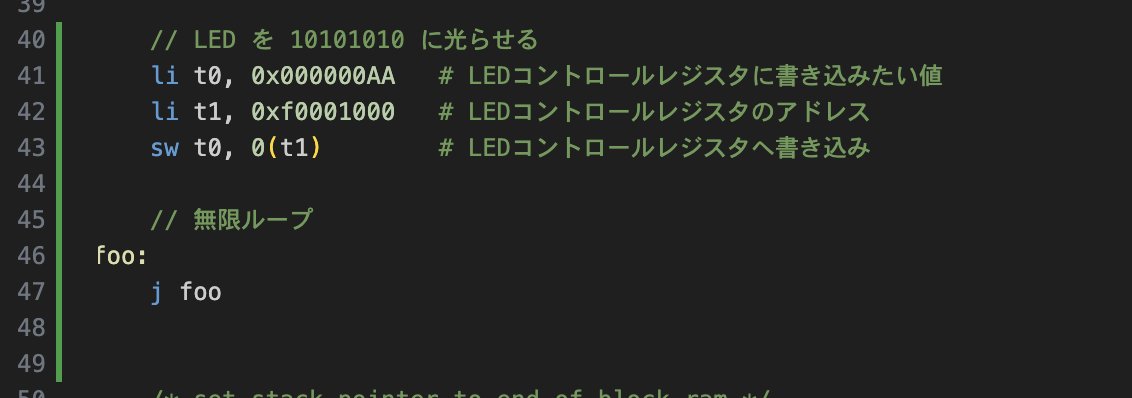

Today's lesson: don't ENABLE_PCPI=1 on PicoRV32 for internal plugins. Thank you to the ever-helpful denizens of @[email protected] Discord for untangling this knotty problem.

Now, I can multiply on Radiona_org - Zagreb Makerspace #ULX3S once more. #FPGA #OSHW